请在线提交您的留言,我们将尽快联系您!

作者:

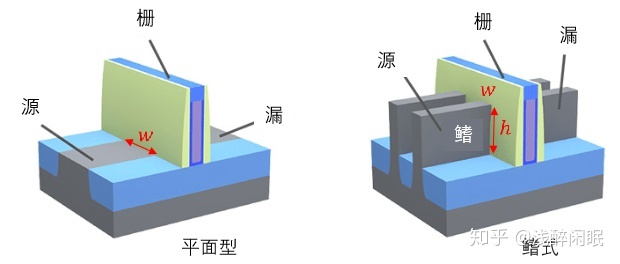

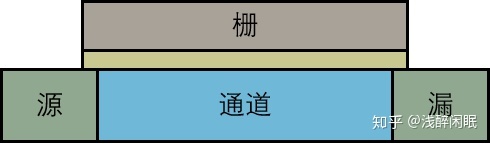

要搞清全环绕栅极技术,我们首先要从场效应晶体管(Field Effect Transistor)说起。所谓的晶体管,是指一种等效于水龙头作用的电子器件。水龙头可以用来控制水流的大小以及开关,与之类似晶体管的作用是控制电流的大小与开关。这里面另外一个关键词是场效应,指的是这种对电流的控制是通过施加一个电场来实现的。如下图所示的晶体管结构中,我们可以 通过对栅极施加一个电压从而在通道内部产生一个电场。这个电场的大小可以被用来调节源极和漏记之间电流的大小。也由此可见,决定场效应晶体管效率的一个重要因素就是栅极对通道的控制能力。

根据电阻的定义 ,我们可以简单估算出源极到漏极之间电阻的大小是和栅极的长度成正比的。栅极越小,在同样的电压下能实现的电流也越大。这是决定晶体管性能的一个关键参数,也因此早期的技术节点往往是根据栅极的长度来命名的。所谓的10微米节点,指的就是栅极的长度最小为10微米。自从引入鳍式晶体管结构之后,技术节点中的数字仅仅是一个营销代号,已经不再和晶体管的任何尺寸直接对应。

上图中另外一个值得注意的地方是通道的长度并不等于栅极的长度。这是因为源极和漏极是通过离子注入(ion-implantation)实现的。在离子注入的过程中,会有离子扩散到栅极下方,形成所谓的扩散层。扩散层的存在,导致了在32纳米节点之后,栅极长度无法进一步缩小(避免漏极和源极之间直接短路)。英特尔也因此在之后的22纳米节点引入了鳍式晶体管。

从平面型晶体管过渡到鳍式晶体管,栅极对通道内电场的控制能力大幅提升。原先栅极与通道的接触面积仅仅是由通道的宽度 决定的,而在鳍式晶体管中则是由 决定。更大的接触面积导致了通道内电流传输的横截面积更大,因而对应的电阻更小电流更高。

鳍式晶体管除了实现对通道更好的控制,另一个重要改进是允许栅极的长度进一步缩小。在平面型晶体管中,源极和漏极的生产是通过离子注入实现的。而在鳍式晶体管中,源极和漏极的则是在栅极做好之后直接在鳍上外延生长(Source-Drain Epitaxy)。此时由于栅极的阻断,不会出现扩散层,也因此不会有短沟效应的问题。

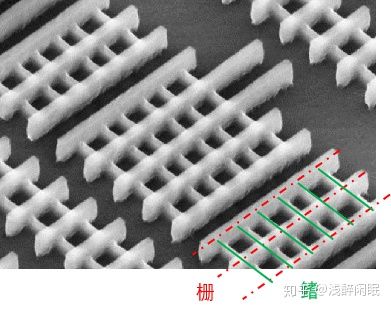

下图是英特尔在22纳米节点首次引入鳍式晶体管时给出的扫描电子显微镜照片。从图中我们可以看到,每一个单元都包含着两组鳍,每组内部各三个。在另外一个方向上,更高的线则是栅线。鳍式晶体管的尺寸缩小的一个重要衡量参数就是鳍线(Fin Line)和栅线(Gate Line)的重复周期。其中鳍线的周期是半导体器件中所有结构中最小的周期,而栅线的周期对整个晶体管的性能有决定性的影响。在22纳米节点,鳍线和栅线的周期分别为60,90纳米。而到了5纳米节点,鳍线和栅线的周期仅为27,54纳米。

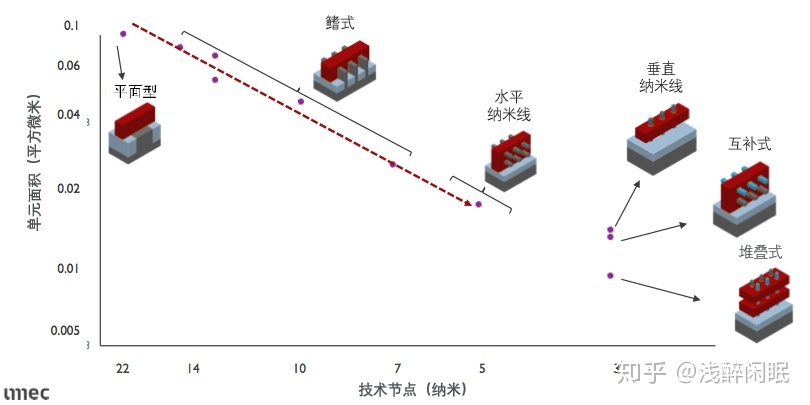

5纳米之后,鳍式晶体管将会面临一系列的问题。首先随着栅线之间的间距进一步减小,很难再像之前那样在一个单元内填充多个鳍线。而如果只做一个鳍线的话,生产工艺又很难保证不同器件之间性能一致。因为控制多个鳍线的平均尺寸要远比控制单个鳍线的尺寸容易得多。其次也是更为致命的问题是,随着栅线之间的间距进一步减小,鳍式晶体管的静电问题急速加剧并直接制约晶体管性能的进一步提升。这里所说的静电问题是指鳍式晶体管本身的结构带来的一系列寄生电容以及电阻的问题。例如栅极与栅极之间的寄生电容,栅极与通道之间的寄生电容,栅极与金属电极之间的寄生电容,以及源极与漏极之间的寄生电阻等问题。IMEC之前的模拟表明,当栅线之间的间距缩小至40纳米之后,鳍式晶体管的性能将会趋于饱和。因此,在5纳米之后,工业界迫切需要一个新的结构来替代鳍式晶体管结构,这就带来了全环绕栅极晶体管。

鳍式晶体管与全环绕栅极的结构对比(图片来源:Samsung)

<span style="color:#999999;font-family:-apple-system, BlinkMacSystemFont, " font-size:14.4px;text-align:center;white-space:normal;background-color:#ffffff;"="">下一代晶体管结构发展(图片来自IMEC)

免责声明|部分素材源自浅醉闲眠,转载仅作为行业分享交流,不代表本司观点,版权归原作者所有。如涉侵权,请联系我们处理。另外,如若转载本文,请标明出处。

如果您对这篇文章感兴趣,请立即联系我们

请在线提交您的留言,我们将尽快联系您!